Development of an AI accelerator model for design space exploration

- Subject:AI accelerators, hardware modeling

- Type:Bachelor thesis

- Tutor:

Development of an AI accelerator model for design space exploration

Context

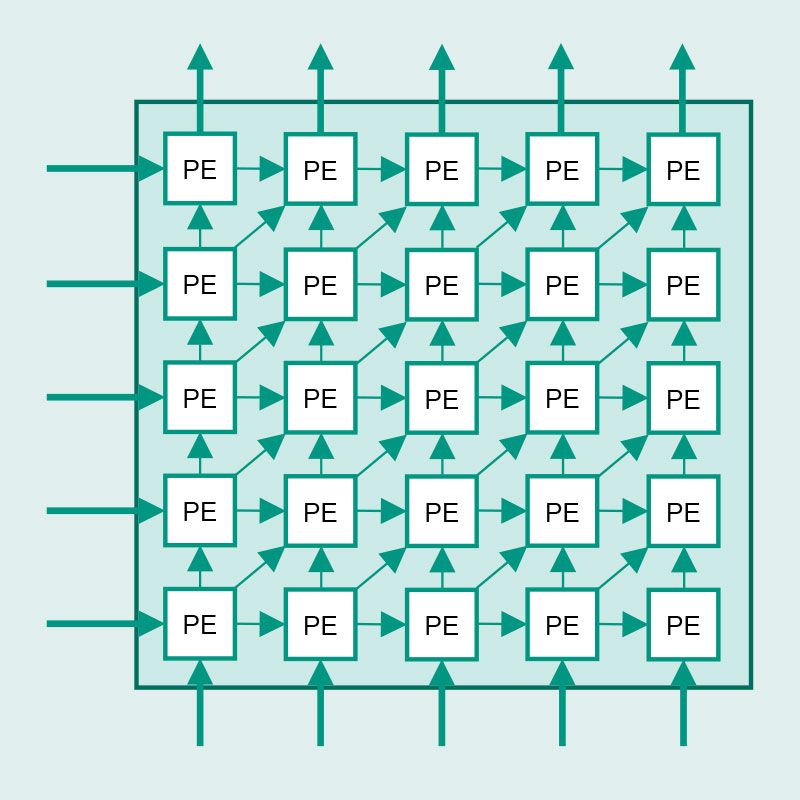

Many modern applications require specialized hardware accelerators to achieve sufficient processing performance. Especially modern AI approaches benefit from dedicated accelerators - but the design depends strongly on the use case. While high performance is achieved by many parallel processing units, only a small chip area is available in embedded systems. Using performance models, the performance of different embodiments of a hardware module can be estimated with little effort and the applicability to different neural networks can be tested.

Tasks

In this thesis, a performance model of an existing CNN accelerator design in SystemC shall be developed. Based on this model, a design space exploration will be performed using common tools from the semiconductor industry (Synopsys Platform Architect), whereby the performance of different designs of the accelerator will be evaluated. To evaluate the model, different types of neural networks are examined for their performance requirements and the behavior of the model is analyzed. Finally, recommendations can be made as to which design parameters (number of units, buffer sizes, etc.) are optimal for specific networks.

Requirements

- Interest in the design of hardware accelerators and SoCs

- Knowledge of VHDL/Verilog as well as C

- Motivation and interest in solving technical problems independently