MLIR Machine-Learning Compiler for RISC-V vector processors

- Subject:ML Compiler mit RISC-V Backend

- Type:Bachelorarbeit

- Date:from 01 / 2025

- Tutor:

- Zusatzfeld:

Thesis at the FZI.

MLIR Machine-Learning Compiler for RISC-V vector processors

Context

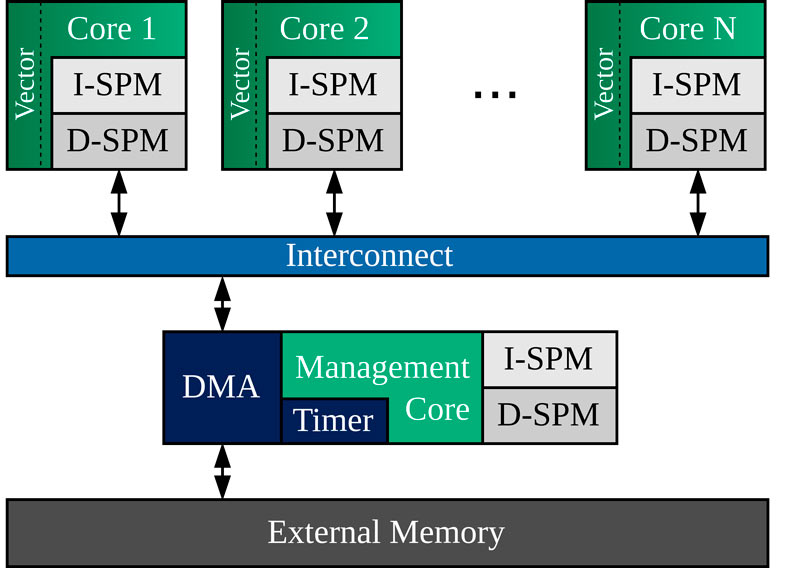

Neural networks are increasingly being used in safety-critical systems such as self-driving cars. It is important to be able to make statements about the time behavior of these systems. For these applications, we at the FZI are developing a hardware accelerator that can execute neural networks efficiently and at the same time has a predictable time behavior. The hardware consists of several RISC-V cores with vector extension and local memory. Communication between the local memories is coordinated via a central management core.

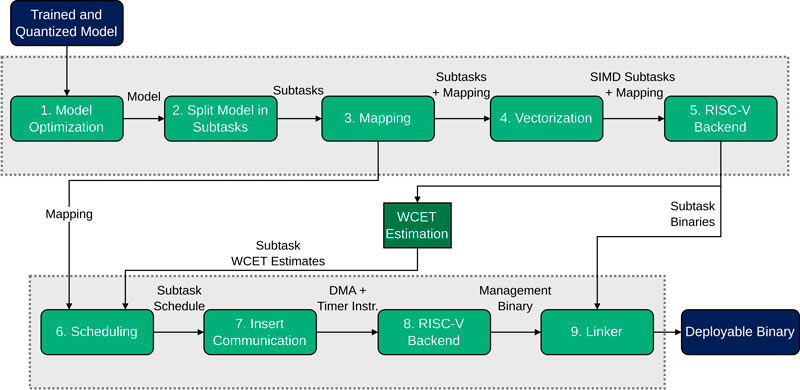

A compiler is required to deploy models on this hardware, which compiles ML models into RISC-V instructions and distributes partial calculations to the various cores.

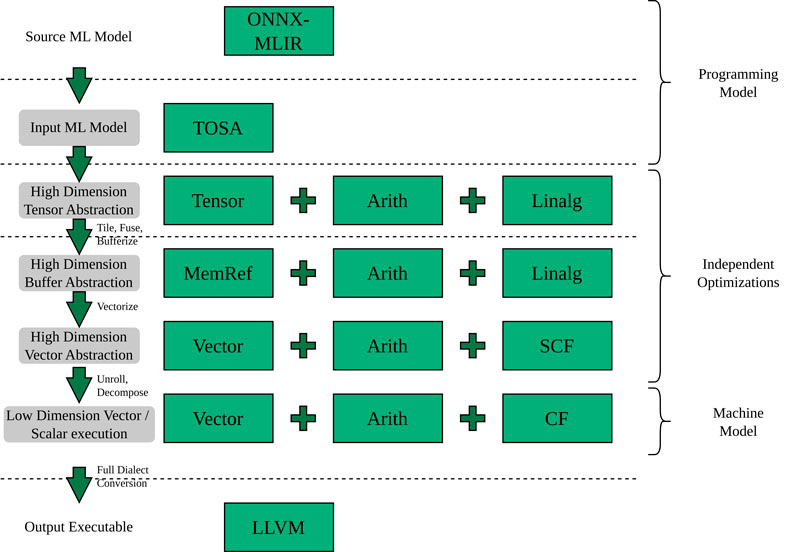

The Multi-Level Intermediate Representation (MLIR) is a modern framework for compiler development, which simplifies extensibility and reusability.

Tasks

State-of-the-art MLIR compilers, such as IREE, BUDDY-MLIR or TT-MLIR, are to be examined within the scope of the work in order to obtain an overview of the methods already available. The main aim of the work is to develop a machine learning compiler that can compile simple ONNX models of CNNs into RISC-V vector instructions. The developed compiler should consist as much as possible of 'upstream' MLIR components. Above all, the compiler should be well structured and extensible in order to be able to add mapping and scheduling components in future work. For evaluation purposes, the generated binaries can be executed in a QEMU environment.

Requirements

- C and C++ programming skills

- Experience in hardware-related programming

- Interest in modern compiler technologies