MLIR Machine-Learning Compiler für RISC-V Vektorprozessoren

- Forschungsthema:ML Compiler mit RISC-V Backend

- Typ:Bachelorarbeit

- Datum:ab 01 / 2025

- Betreuung:

- Zusatzfeld:

Abschlussarbeit am FZI.

MLIR Machine-Learning Compiler für RISC-V Vektorprozessoren

Kontext

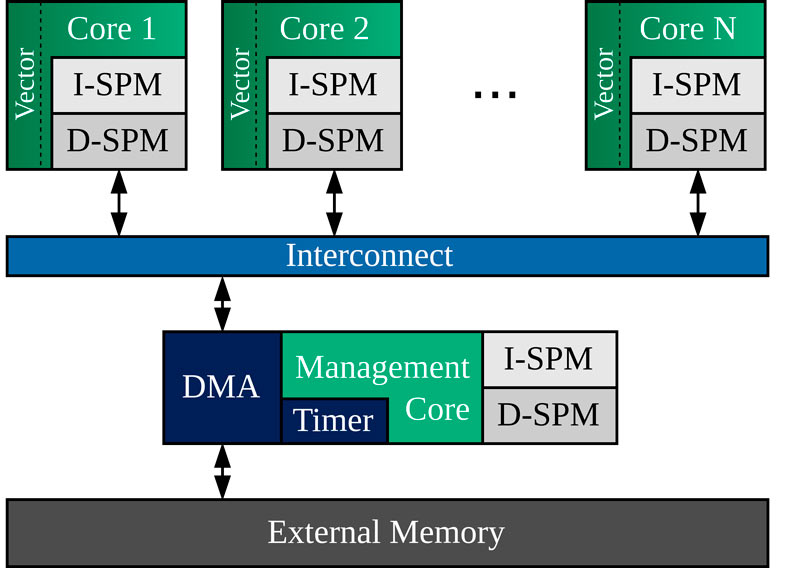

Neuronale Netze werden vermehrt auch in sicherheitskritischen Systemen wie selbstfahrenden Autos eingesetzt. Dabei ist es wichtig, Aussagen über das Zeitverhalten dieser Systeme treffen zu können. Für diese Anwendungen entwickeln wir am FZI einen Hardware Beschleuniger, der Neuronale Netze effizient ausführen kann und gleichzeitig ein vorhersagbares Zeitverhalten aufweist. Die Hardware besteht aus mehreren RISC-V Kernen mit Vektorerweiterung und lokalem Speicher. Die Kommunikation zwischen den lokalen Speichern wird über einen zentralen Management Core koordiniert.

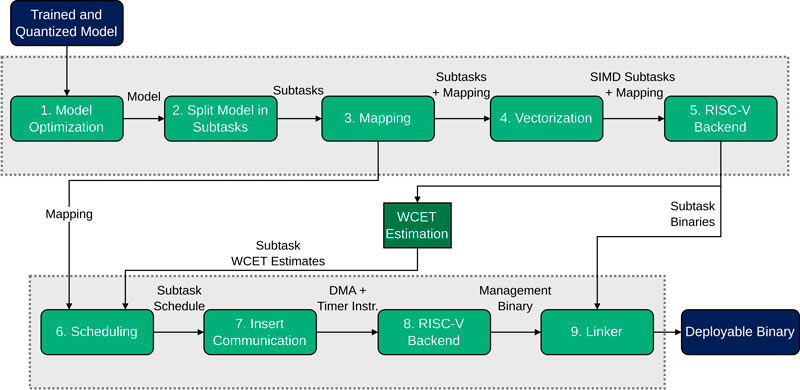

Für das Deployment von Modellen auf dieser Hardware ist ein Compiler nötig, der ML-Modelle zu RISC-V Instruktionen kompiliert und Teilberechnungen auf die verschiedenen Kerne verteilt.

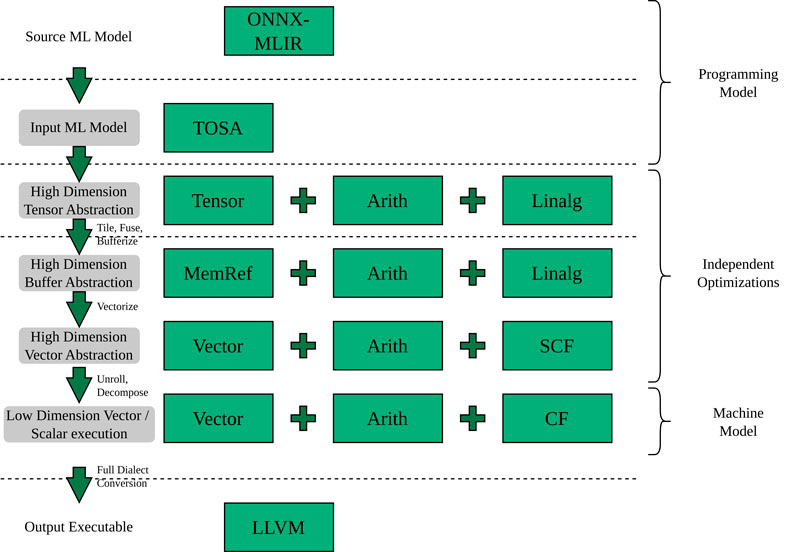

Die Multi-Level Intermediate Representation (MLIR) ist ein modernes Framework für die Compiler Entwicklung, welches Erweiterbarkeit und Wiederverwendbarkeit vereinfacht.

Aufgaben

State-of-the-art MLIR Compiler, wie IREE, BUDDY-MLIR oder TT-MLIR sollen im Rahmen der Arbeit untersucht werden, um einen Überblick über bereits verfügbare Methoden zu erhalten. Hauptsächlich soll im Rahmen der Arbeit ein Machine Learning Compiler entstehen, der einfache ONNX Modelle von CNNs zu RISC-V Vektor Instruktionen kompilieren kann. Der entwickelte Compiler sollte zu möglichst großen Teilen aus ‚upstream‘ MLIR Komponenten bestehen. Der Compiler sollte vor allem gut strukturiert und erweiterbar sein, um in zukünftigen Arbeiten Mapping- und Scheduling- Komponenten hinzufügen zu können. Zur Evaluation können die generierten Binaries in einer QEMU Umgebung ausgeführt werden.

Voraussetzungen

- C und C++ Programmierkenntnisse

- Erfahrungen in hardwarenaher Programmierung

- Interesse an modernen Compiler Technologien