Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

- Institute Director (Spokesman)

- Room: 324

- Phone: +49 721 608-42502

- becker ∂does-not-exist.kit edu

Engesserstr. 5

76131 Karlsruhe

Curriculum Vitae

Jürgen Becker received the Diploma degree in 1992, and his Ph.D. (Dr.-Ing.) degree in 1997, both at Kaiserslautern University, Germany. His research work focused on application development environments for reconfigurable accelerators and included hardware/software codesign, parallelizing compilers, customized computing, and high-level synthesis. He has been local administrator for the European Design Project EUROCHIP in 1993/95. In 1997 Dr. Becker joined the Institute of Microelectronic Systems at Darmstadt University of Technology, Germany, as assistant professor, where he taught CAD algorithms for VLSI design. He did research in Systems-on-Chip (SoC) architectures and reconfigurable technologies for mobile communication systems, including the development of corresponding IP-based CAD methods.

Since 2001 Jürgen Becker is professor for embedded electronic systems at the Institut fuer Technik der Informationsverarbeitung (ITIV) at the University of Karlsruhe. He gives lectures in digital design (undergraduate), in CAD algorithms for high-level synthesis and VLSI design, hardware/software codesign, as well as in bus interfaces and protocols. His actual research is focused on industrial-driven SoCs with emphasis on adaptive embedded systems, e.g. dynamically reconfigurable hardware architectures. This includes corresponding hardware/software codesign and co-synthesis techniques from high-level specifications, as well as low power SoC optimization. Prof. Becker is co-director of the Embedded Systems and Sensors Engineering (ESS) group at the Computer Science Research Center (FZI).

He is author and co-author of more than 400 scientific papers (+ more than 30 patents), published in peer-reviewed international journals and conferences and active in several technical program and steering committees of international conferences and workshops. Prof. Becker started in October 2004 as Vice President of Universität Karlsruhe (TH) responsible for the area Studies and Teaching, respectively since October 2009 to March 2012 as Chief Higher Education Officer (CHEO) of the KIT.

From 2012 until 2014 he serves as Secretary General of CLUSTER, an association of 12 leading technical universities in Europe.

In 2013 Prof. Becker received the Honorary Doctor award (Dr. h. c.) from Technical University Budapest (Hungary).

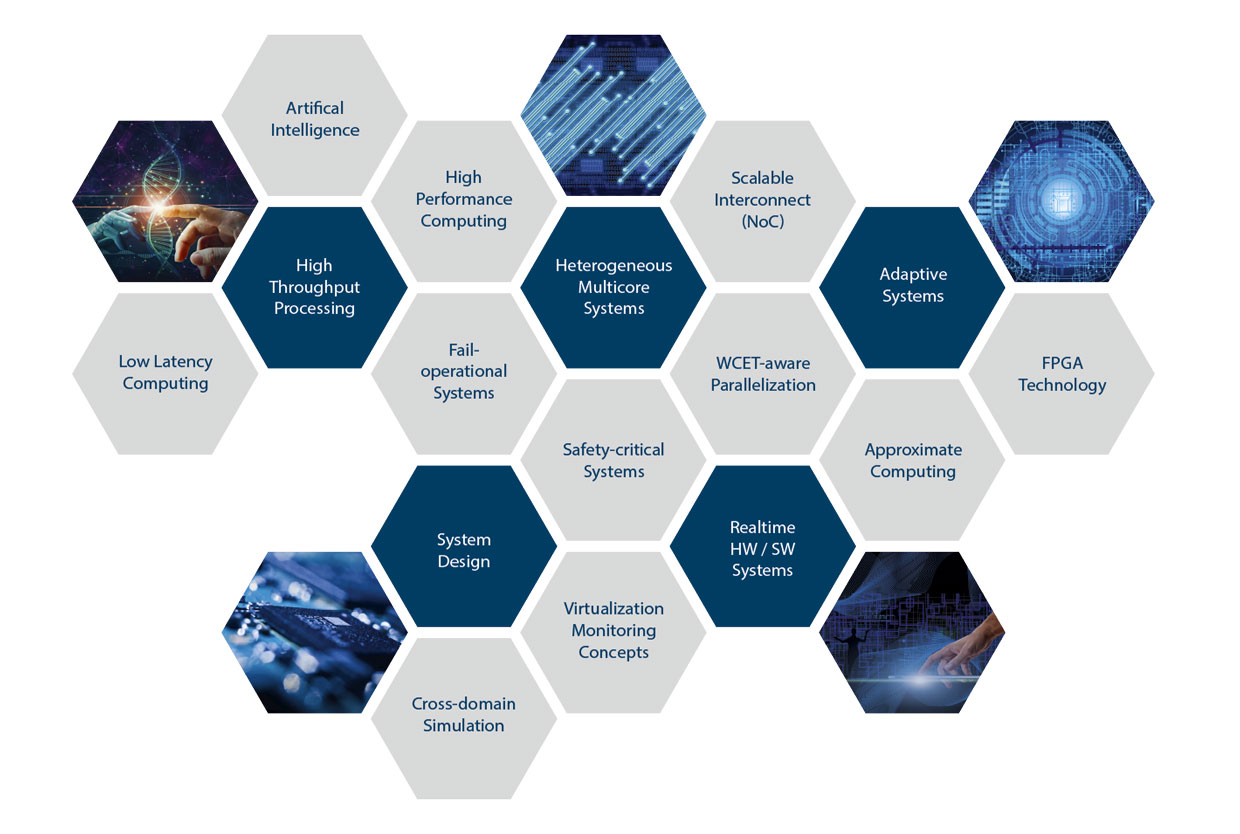

Head of the research area "Embedded Electronic Systems" with the research focus on

- System-on-Chip (SoC), Network-on-Chip (NoC)

- Hardware Software Codesign

- Multi-Core Processor Architectures

- HPC- & KI-based System Integration

- Specific Accelerators

- Reliability, Real-time and Power

- Dynamic Reconfigurable Systems

- Hardware Synthesis Methods and Multi-Domain Modeling & Simulation Techniques

- Cyber-Physical Systems (CPS)

Head of the Embedded Systems and Sensors Engineering (ESS) department at the FZI

| Occasion |

|---|

| State Teaching Prize |

| Honorary Doctorate from TWU Budapest |

| Robert Piloty Prize of the TU Darmstadt |

Executive functions and roles

- Lecturer at the Hector School of Engineering and Management (Technical Business School of the KIT)

- Managing Director of the International Department at the University of Karlsruhe (TH) (2002-2005)

- Vice-Rector for Studies and Teaching at the University of Karlsruhe (TH) (2005-2009)

- Member of the Executive Board of the German Section of the IEEE and Counselor of the IEEE Student Branch at KIT (2006-today)

- Managing Director of the University Didactics Center Baden-Württemberg (2007-2012)

- Chief Higher Education Officer (CHEO) of the KIT (2009-2012)

- Director at the Research Center for Information Technology(FZI) in the Embedded Systems and Sensors Engineering(ESS) research group

- Dean of Studies NwT(https://www.sle.kit.edu/vorstudium/lehramt-nwt.php)(until 2017)

- Member of the HoC Board of Directors (House of Competence) (until 2017)

- Member of the KSETA Scientific Council (Karlsruhe School of Elementary Particle and Astroparticle Physics)

- Member of the KCETA Steering Committee (KIT Center for Elementary Particle and Astroparticle Physics)

- Coordinator KIT / KIC EIThealth

- Secretary General CLUSTER (until 2014) (consortium of 12 universities)

Conferences

- FPL (International Conference on Field-Programmable Logic and Applications)

- RAW (Reconfigurable Architecture Workshop)

- ARC (International Symposium on Applied Reconfigurable Computing)

- ISVLSI (IEEE Computer Society Annual Symposium on VLSI)

- IEEE SOCC (IEEE International System-on-Chip Conference)

- PATMOS (International Workshop on Power And Timing Modeling, Optimization and Simulation)

Projects (selection)

|

XANDAR project Software and hardware for networked embedded systems must meet the highest requirements in terms of safety, real-time capability, energy and resource efficiency. In the XANDAR project, eight partners from science and industry are developing a complete toolchain for software development and hardware-software integration for complex applications on future processor platforms, for example in autonomous vehicles and for future urban air mobility concepts. |

|

|

ARAMiS II project Future safety-critical applications in the automotive and aviation industries, as well as the future topic of Industry 4.0, show a significant increase in demand for digital computing power. |

|

|

ARAMiS project ARAMiS (Automotive, Railway and Avionics Multicore Systems) aims to create the technological basis for further increasing safety, traffic efficiency and comfort through the use of multicore technology in the mobility domains of automotive, avionics and railroad. |

|

|

Open6G Hub 6G represents wireless communication in our future highly networked world. It enables the networking of autonomous devices, vehicles and drones and creates the basis for the high communication bandwidths required in the future. Within the Open 6G Hub project, the development of a global 6G standard is being driven forward in order to take social priorities into account and to strengthen the position of Germany and Europe in the international competition for 6G. |

|

CeCaS - Central Car Server Automated, connected and electrified vehicles are picking up speed. However, energy-efficient and cost-effective high-end compute platforms that can keep pace with the requirements in terms of computing power and complexity with full automotive qualification (ASIL-D) are lacking for full suitability for everyday use. AI-based areas in particular, such as autonomous driving, require customized, real-time capable and energy-efficient high-performance processors. It's all about performance and safety from a single source - and the future viability of the automotive industry. |

|

EMDRIVE The overarching goal of EMDRIVE is a hierarchical, scalable platform concept for distributed heterogeneous automotive real-time computing network architectures - Centralized High-Performance Automotive RT-Compute Boardnets (Sensor2Edge). The results are to be incorporated into automotive production beyond the project. |

|

BELLE II The Belle II experiment in Tsukuba, Japan offers unique opportunities to study rare τ decays and to study certain forms of dark photons and physics beyond the standard model. For this purpose, electrons and their protons are accelerated to almost the speed of light in the asymmetric SuperKEKB in order to collide them in the Belle II detector. The resulting decay products are measured and recorded in order to analyze the data later. It is important to distinguish interesting new data from already known decays. To ensure this, a two-stage trigger system is installed to analyze all decays. The first stage consists of a pipelined, dead time-free FPGA system. The second stage, on the other hand, is calculated on mainframe computers using software. |

Innovation

| title | short description |

|---|---|

| Hochleistungsrechner steuern Autos der Zukunft – das Projekt CeCaS | Specialist article in HI:TECH CAMPUS magazine |

| LVNr. | Titel | Typ | Semester |

|---|---|---|---|

| 2311616 | Communication Systems and Protocols | Lecture (V) | SS 2025 |

| 2311645 | Digital Hardware Design Laboratory | Praktikum (P) | SS 2025 |

| 2311615 | Digital technology / Basics of digital technology | Lecture (V) | WS 24/25 |

| 2311608 | Hardware Modeling and Simulation | Lecture (V) | WS 24/25 |

| 2311619 | Hardware Synthesis and Optimization | Lecture (V) | SS 2025 |

| 2311620 | Hardware/Software Co-Design | Lecture (V) | WS 24/25 |

| 2311612 | Laboratory System-on-Chip | Praktikum (P) | WS 24/25 |

| 2311638 | Laboratory circuit design | Praktikum (P) | |

| 2311650 | Laboratory for Applied Machine Learning Algorithms | Praktikum (P) | WS 24/25 |

| 2311637 | Laboratory in Design Automation | Praktikum (P) | SS 2025 |

| 2311627 | Seminar Embedded Systems | Seminar (S) | SS 2025 |

| 2311628 | Seminar Fundamentals of Embedded Systems | Seminar (S) | SS 2025 |

Publications

Unger, K. L.; Becker, J.; Forsthofer, T.; Hiesl, S.; Kiesling, C.; Neu, M.; Schmidt, E.; Meggendorfer, F.; Mi, T.; Ou, Z.

2025. Journal of Instrumentation, 20 (02), Art.-Nr.: C02051. doi:10.1088/1748-0221/20/02/C02051

Bähr, S.; Bae, H.; Becker, J.; Bertemes, M.; Campajola, M.; Ferber, T.; Forsthofer, T.; Hiesl, S.; Inguglia, G.; Iwasaki, Y.; Jülg, T.; Kiesling, C.; Knoll, A. C.; Koga, T.; Lai, Y.-T.; Lenz, A.; Liu, Y.; Meggendorfer, F.; Nakazawa, H.; Neu, M.; et al.

2025. Nuclear Instruments and Methods in Physics Research, Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 1073, 170279. doi:10.1016/j.nima.2025.170279

Mazza, G.; Calvo, D.; Cossio, F.; De Remigis, P.; Lenta, F.; Mignone, M.; Wheadon, R.; Becker, J.; Brinkmann, K. T.; Caselle, M.; Kopmann, A.; Manzhura, O.; Peter, M.; Sidorenko, V.; Stanek, P.; Stockmanns, T.; Tomasek, L.; Troll, N.; Unger, K. L.; Zaunick, H. G.

2025. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 1071, 170069. doi:10.1016/j.nima.2024.170069

Nuss, B.; Karle, C.; Neu, M.; Witte, L.; Scheder, A.; Franchi, N.; Vossiek, M.; Becker, J.; Zwick, T.

2025. European Wireless 2024 : 29th European Wireless Conference September 09 – 11, 2024 in Brno, Czech Republic, 187–192, VDE Verlag

Kreß, F.

2025, March 18. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000180033

Becker, J.; Wolf, M.

2024. IEEE Design & Test, 41 (6), 97–100. doi:10.1109/MDAT.2024.3443829

Bannwart Perina, A.; Becker, J.; Bonato, V.

2024. Journal of Signal Processing Systems, 96 (11), 651–671. doi:10.1007/s11265-024-01938-3

Balaskas, K.; Khdr, H.; Bakr Sikal, M.; Kreß, F.; Siozios, K.; Becker, J.; Henkel, J.

2024. IEEE Embedded Systems Letters, 16 (4), 317–320. doi:10.1109/LES.2024.3443628

PANDA collaboration; Caselle, M.; Manzhura, O.; Calvo, D.; Dellacasa, G.; Chilingaryan, S.; Cossio, F.; Kopmann, A.; Lenta, F.; Mazza, G.; Peter, M.; Sidorenko, V.; Stockmanns, T.; Tröll, N.; Unger, K. L.; Zaunick, H.-G.; Becker, J.; Brinkmann, K.-T.

2024. Journal of Instrumentation, 19 (12), C12015. doi:10.1088/1748-0221/19/12/C12015

Bauer, L.; Nassar, H.; Khan, N.; Becker, J.; Henkel, J.

2024. IEEE Transactions on Circuits and Systems for Artificial Intelligence, 1 (2), 178–190. doi:10.1109/TCASAI.2024.3483118

Lenta, F.; Calvo, D.; Cossio, F.; Mazza, G.; Wheadon, R.; Becker, J.; Brinkmann, K.-T.; Caselle, M.; Kopmann, A.; Manzhura, O.; Mattiazzo, S.; Peter, M.; Sidorenko, V.; Staněk, P.; Stockmanns, T.; Tomášek, L.; Tröll, N.; Unger, K. L.; Zaunick, H.-G.

2024. Journal of Instrumentation, 19 (04), Art.-Nr.: C04047. doi:10.1088/1748-0221/19/04/C04047

Manzhura, O.; Caselle, M.; Ardila-Perez, L. E.; Calvo, D.; Chilingaryan, S.; Cossio, F.; Dritschler, T.; Kopmann, A.; Lenta, F.; Mazza, G.; Peter, M.; Sidorenko, V.; Staněk, P.; Stockmanns, T.; Tomášek, L.; Tröll, N.; Unger, K. L.; Zaunick, H.-G.; Becker, J.; Brinkmann, K.-T.

2024. Journal of Instrumentation, 19 (03), Art.-Nr.: C03036. doi:10.1088/1748-0221/19/03/C03036

CBM Collaboration; Sidorenko, V.; Müller, W. F. J.; Emschermann, D.; Zabolotny, W.; Fröhlich, I.; Becker, J.

2024. Journal of Instrumentation, 19 (03), Art.-Nr.: C03014. doi:10.1088/1748-0221/19/03/C03014

Neu, M.; Becker, J.; Dorwarth, P.; Ferber, T.; Reuter, L.; Stefkova, S.; Unger, K.

2024. Computing and Software for Big Science, 8 (1), Artl.Nr.: 8. doi:10.1007/s41781-024-00117-0

Mühlbeier, E.; Bauer, V.; Schade, F.; Gönnheimer, P.; Becker, J.; Fleischer, J.

2024. 56th CIRP International Conference on Manufacturing Systems 2023 Hrsg.: Mpofu, Khumbulani; Sacks, Natasha; Damm, Oliver, 120, 744–749. doi:10.1016/j.procir.2023.09.069

Kirschner, M.; Dudzikk, K.; Becker, J.

2024. 2024 IEEE Real-Time Systems Symposium (RTSS), 427 – 430, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/RTSS62706.2024.00043

Schmidt, P.; Topko, I.; Stammler, M.; Harbaum, T.; Becker, J.; Berner, R.; Ahmed, O.; Jagielski, J.; Seidler, T.; Abel, M.; Kreutzer, M.; Kirschner, M.; Betancourt, V. P.; Sehm, R.; Groth, L.; Neskovic, A.; Meyer, R.; Mulhem, S.; Berekovic, M.; Probst, M.; et al.

2024. 27th Design, Automation and Test in Europe Conference and Exhibition (DATE 2024), 6 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE58400.2024.10546796

Topko, I.; Harbaum, T.; Becker, J.

2024. 2024 IEEE Nordic Circuits and Systems Conference (NorCAS). Ed.: J. Nurmi, 7 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NorCAS64408.2024.10752456

Vasilache, A.; Krausse, J.; Knobloch, K.; Becker, J.

2024. 2024 IEEE Biomedical Circuits and Systems Conference (BioCAS), Xi’an, 24th-26th October 2024, 1–5, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/BioCAS61083.2024.10798246

Serdyuk, A.; Kreß, F.; Topko, I.; Harbaum, T.; Becker, J.; Hamann, T.; Kämpf, P.

2024. 2024 Sensor Data Fusion: Trends, Solutions, Applications (SDF), Bonn, Germany, 25-27 November 2024, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SDF63218.2024.10773805

Krausse, J.; Nitzsche, S.; Pachideh, B.; Weigelt, C.; Knobloch, K.; Becker, J.

2024. 2024 International Conference on Neuromorphic Systems (ICONS), Arlington, 30th July 2024 - 2nd August 2024, 140–147, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ICONS62911.2024.00028

Schmidt, P.; Pfau, J.; Hotfilter, T.; Stammler, M.; Harbaum, T.; Becker, J.

2024. 2024 IEEE 37th International System-on-Chip Conference (SOCC), Dresden, 16th-19th September 2024, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737723

Krausse, J.; Neher, M.; Fuerst-Walter, I.; Weigelt, C.; Harbaum, T.; Knobloch, K.; Becker, J.

2024. 2024 IEEE 37th International System-on-Chip Conference (SOCC), Dresden, 16th-19th September 2024, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737770

Stammler, J. M.; Hoefer, J.; Schmidt, P.; Harbaum, T.; Becker, J.

2024. 2024 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 656 – 660, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI61997.2024.00125

Neu, M.; Karle, C.; Schmidt, P.; Höfer, J.; Harbaum, T.; Becker, J.

2024. IEEE 37th International System-on-Chip Conference (SOCC 2024), 6 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737798

Karle, C.; Neu, M.; Nuss, B.; Witte, L.; Scheder, A.; Waldner, E.; Shkurtaj, E.; Harbaum, T.; Becker, J.

2024. IEEE 37th International System-on-Chip Conference (SOCC 2024), 6 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737777

Karle, C.; Neu, M.; Nuss, B.; Chen, J.; Witte, L.; Scheder, A.; Harbaum, T.; Becker, J.

2024. IEEE 37th International System-on-Chip Conference (SOCC 2024), 6 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737765

Kreß, F.; Serdyuk, A.; Kobsar, D.; Hotfilter, T.; Höfer, J.; Harbaum, T.; Becker, J.

2024. 2024 IEEE 37th International System-on-Chip Conference (SOCC), Dresden, Germany, 16-19 September 2024, 126–131, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737863

Kreß, F.; El Annabi, E. M.; Hotfilter, T.; Hoefer, J.; Harbaum, T.; Becker, J.

2024. 2024 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 1st-3rd July 2024, Knoxville, 39–44, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI61997.2024.00019

Alagi, H.; Fischer, N.; Behrends, K.; Ftirst-Walter, I.; Becker, J.; Beigl, M.; Mathis-Ullrich, F.; Hein, B.

2024. 2024 10th IEEE RAS/EMBS International Conference for Biomedical Robotics and Biomechatronics (BioRob), Heidelberg, Germany, 01-04 September 2024, 889–894, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/BioRob60516.2024.10719794

Kreß, F.; Sidorenko, V.; Topko, I.; Unger, K.; Harbaum, T.; Becker, J.

2024. 2024 IEEE 3rd German Education Conference (GECon), Munich, Germany, 05-07 August 2024, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/GECon62014.2024.10734007

Schmidt, P.; Becker, J.

2024. 2024 IEEE 32nd Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), Orlando, 5th-8th May 2024, 241 – 242, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/FCCM60383.2024.00055

Dörr, T.; Schade, F.; Becker, J.; Keramidas, G.; Petrellis, N.; Kelefouras, V.; Mavropoulos, M.; Antonopoulos, K.; Antonopoulos, C. P.; Voros, N.; Ahlbrecht, A.; Zaeske, W.; Janson, V.; Nöldeke, P.; Durak, U.; Panagiotou, C.; Karadimas, D.; Adler, N.; Reichmann, C.; Sailer, A.; et al.

2024. Design, Automation & Test in Europe Conference & Exhibition (DATE), Valencia, Spain, 25-27 March 2024, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE58400.2024.10546852

Gutermann, A.; Becker, J.

2024. 2024 IEEE 35th International Conference on Application-specific Systems, Architectures and Processors (ASAP), Hong Kong, 24th-26th July 2024, 226 – 227, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ASAP61560.2024.00052

Lesniak, F.; Gutermann, A.; Harbaum, T.; Becker, J.

2024. GLSVLSI ’24: Proceedings of the Great Lakes Symposium on VLSI 2024, 151 – 157, Association for Computing Machinery (ACM). doi:10.1145/3649476.3658737

Hoefer, J.; Gauß, M.; Adams, M.; Kreß, F.; Kempf, F.; Karle, C.; Harbaum, T.; Barth, A.; Becker, J.

2024. 2024 IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, Singapore, 19-22 May 2024, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISCAS58744.2024.10557955

Serdyuk, A.; Kreβ F.; Hiegle, M.; Harbaum, T.; Becker, J.; Imbert, F.; Soullard, Y.; Tavenard, R.; Anquetil, E.; Barth, J.; Kämpf, P.

2024. 2023 IEEE 9th World Forum on Internet of Things (WF-IoT), Aveiro, 12th - 27th October 2023, 01–06, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/WF-IoT58464.2023.10539488

Harbaum, T.; Topko, I.; Serdyuk, A.; Fürst-Walter, I.; Kreß, F.; Becker, J.

2024. 3rd Workshop on Deep Learning for IoT (DL4IoT-2024)

Schade, F.; Dörr, T.; Ahlbrecht, A.; Janson, V.; Durak, U.; Becker, J.

2024. 2023 26th Euromicro Conference on Digital System Design (DSD), Golem, 6th - 8th September 2023, 436 – 443, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD60849.2023.00067

Stammler, M.; Hamann, M.; Harbaum, T.; Becker, J.

2024. 2023 26th Euromicro Conference on Digital System Design (DSD), Golem, 6th - 8th September 2023, 561 – 568, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD60849.2023.00083

Lesniak, F.; Harbaum, T.; Becker, J.

2024. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), Singapur, 18th - 21st December 2023, 340–346, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00057

Stammler, M.; Sidorenko, V.; Kreß, F.; Schmidt, P.; Becker, J.

2024. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), Singapur, 18th-21st December 2023, 97–104, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00022

Mostafa, J.; Melissano, S.; Chilingaryan, S.; Kopmann, A.; Becker, J.

2024. doi:10.5281/zenodo.10580527

Kreß, F.; Sidorenko, V.; Topko, I.; Unger, K.; Schneider, M.; Becker, J.

2024

Kreß, F.; Sidorenko, V.; Topko, I.; Unger, K.; Schneider, M.; Becker, J.

2024

Kreß, F.; Sidorenko, V.; Topko, I.; Unger, K.; Schneider, M.; Becker, J.

2024

Kreß, F.; Sidorenko, V.; Topko, I.; Unger, K.; Schneider, M.; Becker, J.

2024

Kreß, F.; Sidorenko, V.; Topko, I.; Unger, K.; Schneider, M.; Becker, J.

2024

Kreß, F.; Sidorenko, V.; Topko, I.; Unger, K.; Schneider, M.; Becker, J.

2024

Kreß, F.; Sidorenko, V.; Topko, I.; Unger, K.; Schneider, M.; Becker, J.

2024

Kreß, F.; Sidorenko, V.; Topko, I.; Unger, K.; Schneider, M.; Becker, J.

2024

Kreß, F.; Sidorenko, V.; Topko, I.; Unger, K.; Schneider, M.; Becker, J.

2024

Wolf, O.

2024, November 14. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000176033

Dörr, T.

2024, October 28. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000175388

Pfau, J.

2024, November 15. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000174452

Lu, Z.

2024, August 21. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000173484

Hotfilter, T.

2024, August 14. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000173259

Schade, F.

2024, July 23. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000172536

Unger, K.; Becker, J.; Kiesling, C.; Ma, Y.; Meggendorfer, F.; Neu, M.; Schmidt, E.; Zweigart, U.

2023. Applied Reconfigurable Computing. Architectures, Tools, and Applications – 19th International Symposium, ARC 2023, Cottbus, Germany, September 27–29, 2023, Proceedings. Ed.: F. Palumbo, 173–184, Springer Nature Switzerland. doi:10.1007/978-3-031-42921-7_12

Schade, F.; Kreutzer, M.; Mühlbeier, E.; Gerlitz, E.; Gönnheimer, P.; Fleischer, J.; Becker, J.

2023. Procedia CIRP, 120, 601–606. doi:10.1016/j.procir.2023.09.045

Stammler, M.; Höfer, J.; Kraus, D.; Schmidt, P.; Hotfilter, T.; Harbaum, T.; Becker, J.

2023. Procedia Computer Science, 222, 499 – 508. doi:10.1016/j.procs.2023.08.188

Kreß, F.; Sidorenko, V.; Schmidt, P.; Hoefer, J.; Hotfilter, T.; Walter, I.; Harbaum, T.; Becker, J.

2023. Computer Networks, 229, Article no: 109759. doi:10.1016/j.comnet.2023.109759

Sidorenko, V.; Müller, W. F. J.; Zabolotny, W.; Fröhlich, I.; Emschermann, D.; Becker, J.

2023. Journal of Instrumentation, 18 (2), Art.-Nr.: C02052. doi:10.1088/1748-0221/18/02/C02052

Unger, K. L.; Bähr, S.; Becker, J.; Knoll, A. C.; Kiesling, C.; Meggendorfer, F.; Skambraks, S.

2023. Journal of Physics: Conference Series, 2438, Article no: 012056. doi:10.1088/1742-6596/2438/1/012056

Unger, K. L.; Neu, M.; Becker, J.; Schmidt, E.; Kiesling, C.; Meggendorfer, F.; Skambraks, S.

2023. Journal of Instrumentation, 18 (2), Art.-Nr.: C02001. doi:10.1088/1748-0221/18/02/C02001

Kempf, F.; Hoefer, J.; Harbaum, T.; Becker, J.; Fasfous, N.; Frickenstein, A.; Voegel, H.-J.; Friedrich, S.; Wittig, R.; Matúš, E.; Fettweis, G.; Lueders, M.; Blume, H.; Benndorf, J.; Grantz, D.; Zeller, M.; Engelke, D.; Eickel, K.-H.

2023. 2023 Design, Automation & Test in Europe Conference & Exhibition (DATE), Antwerp, Belgium, 17-19 April 2023, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE56975.2023.10137257

Kreß, F.; Serdyuk, A.; Hiegle, M.; Waldmann, D.; Hotfilter, T.; Hoefer, J.; Hamann, T.; Barth, J.; Kämpf, P.; Harbaum, T.; Becker, J.

2023. 26th Euromicro Conference on Digital System Design (DSD 2023), 569–576, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD60849.2023.00084

Anantharajaiah, N.; Lesniak, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), 38 – 44, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00014

Kempf, F.; Höfer, J.; Hotfilter, T.; Becker, J.

2023. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), 276 – 283, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00048

Fürst-Walter, I.; Nappi, A.; Harbaum, T.; Becker, J.

2023. 2023 IEEE/RSJ International Conference on Intelligent Robots and Systems (IROS), Detroit, Mi, 1st-5th October 2023, 10888 – 10893, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/IROS55552.2023.10341256

Pfau, J.; Hernandez, J.; Reuter, M.; Hofmann, K.; Becker, J.

2023. 2023 IEEE Nordic Circuits and Systems Conference (NorCAS), Aalborg, 31st October - 01st November 2023, 7 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NorCAS58970.2023.10305486

Hotfilter, T.; Hoefer, J.; Merz, P.; Kreß, F.; Kempf, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 36th International System-on-Chip Conference (SOCC), Santa Clara, USA, 05-08 September 2023, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC58585.2023.10256738

Pachideh, B.; Zielke, C.; Nitzsche, S.; Becker, J.

2023. 2023 IEEE 36th International System-on-Chip Conference (SOCC), Santa Clara, USA, 05-08 September 2023, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC58585.2023.10257066

Hofman, D.; Brcic, M.; Kovac, M.; Hotfilter, T.; Becker, J.; Reinhardt, D.; Grigorescu, S. M.; Stevens, R.; Vo, T. T.

2023. 2023 IEEE 36th International System-on-Chip Conference (SOCC), Santa Clara, USA, 05-08 September 2023, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC58585.2023.10257105

Lesniak, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 36th International System-on-Chip Conference (SOCC), Santa Clara, USA, 05-08 September 2023, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC58585.2023.10257090

Kreß, F.; Pfau, J.; Kempf, F.; Schmidt, P.; He, Z.; Harbaum, T.; Becker, J.

2023. 2023 IEEE Nordic Circuits and Systems Conference (NorCAS), 31st October - 1st November 2023, Aalborg, Denmark, 1–7, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NorCAS58970.2023.10305469

Gönnheimer, P.; Ströbel, R.; Roßkopf, A.; Dörflinger, R.; Walter, I.; Becker, J.; Fleischer, J.

2023. 16th CIRP Conference on Intelligent Computation in Manufacturing Engineering CIRP ICME ‘22, Italy. Hrsg.: R. Teti, D. D’Addona, 145 – 150, Elsevier. doi:10.1016/j.procir.2023.06.026

Anantharajaiah, N.; Xu, Y.; Lesniak, F.; Harbaum, T.; Becker, J.

2023. IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI59464.2023.10238569

Nuss, B.; Groeschel, P.; Pfau, J.; Becker, J.; Vossiek, M.; Zwick, T.

2023. European Wireless 2022 ; 27th European Wireless Conference, Dresden, 19th - 21st September 2022, 89 – 91, VDE VERLAG GMBH

Hoefer, J.; Hotfilter, T.; Kreß, F.; Qiu, C.; Harbaum, T.; Becker, J.

2023. Computer Vision Systems – 14th International Conference, ICVS 2023, Vienna, Austria, September 27–29, 2023. Ed.: H. Christensen, 299–309, Springer Nature Switzerland. doi:10.1007/978-3-031-44137-0_25

Dörr, T.; Schade, F.; Becker, J.

2023. Computer Safety, Reliability, and Security. Ed.: J. Guiochet, 181–195, Springer Nature Switzerland. doi:10.1007/978-3-031-40923-3_14

Neu, M.; Karle, C.; Nuss, B.; Groeschel, P.; Becker, J.

2023. 2023 19th International Conference on Distributed Computing in Smart Systems and the Internet of Things (DCOSS-IoT), 171–178, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DCOSS-IoT58021.2023.00039

Hotfilter, T.; Höfer, J.; Kreß, F.; Kempf, F.; Kraft, L.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 5th International Conference on Artificial Intelligence Circuits and Systems (AICAS), 1–5, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/AICAS57966.2023.10168566

Marten, J. C.; Younis, M.; Krieger, G.; Pfau, J.; Unger, K.; Becker, J.

2023. 24th International Radar Symposium (IRS), Berlin, Germany, 24-26 May 2023, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/IRS57608.2023.10172405

Pfau, J.; Leys, R.; Neu, M.; Serdyuk, A.; Peric, I.; Becker, J.

2023. 2023 IEEE International Symposium on Circuits and Systems (ISCAS), 5 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISCAS46773.2023.10181679

Chu, A.; Hermann, C. M.; Silz, J.; Pfau, J.; Barón, K. M.; Anantharajaiah, N.; Schmidt, P.; Hotfilter, T.; Xie, X.; Becker, J.; Kallfass, I.; Roth-Stielow, J.; Stork, W.

2023. IEEE EUROCON 2023 - 20th International Conference on Smart Technologies, 665–670, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/EUROCON56442.2023.10199076

Stammler, M.; Hamann, M.; Becker, J.

2023. 2023 12th Mediterranean Conference on Embedded Computing (MECO), 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MECO58584.2023.10154914

Karle, C.; Neu, M.; Pfau, J.; Sperling, J.; Becker, J.

2023. 2023 IEEE 31st Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 08-11 May 2023, Marina Del Rey, CA, USA, 209, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/FCCM57271.2023.00037

Kempf, F.; Becker, J.

2023. 2023 12th Mediterranean Conference on Embedded Computing (MECO), 1–5, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MECO58584.2023.10154986

Hoefer, J.; Kempf, F.; Hotfilter, T.; Kreß, F.; Harbaum, T.; Becker, J.

2023. Proceedings of the Great Lakes Symposium on VLSI 2023, 287–292, Association for Computing Machinery (ACM). doi:10.1145/3583781.3590226

Betancourt, V. P.; Kirschner, M.; Kreutzer, M.; Becker, J.

2023. 2023 IEEE 15th International Symposium on Autonomous Decentralized System (ISADS), 8 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISADS56919.2023.10092022

Lesniak, F.; Anantharajaiah, N.; Harbaum, T.; Becker, J.

2023. RAPIDO ’23: Proceedings of the DroneSE and RAPIDO: System Engineering for constrained embedded systems, 31–38, Association for Computing Machinery (ACM). doi:10.1145/3579170.3579262

Hotfilter, T.; Schmidt, P.; Höfer, J.; Kreß, F.; Harbaum, T.; Becker, J.

2023. DroneSE and RAPIDO: System Engineering for constrained embedded systems, 73–78, Association for Computing Machinery (ACM). doi:10.1145/3579170.3579258

Sandmann, T.; Becker, J.

2023. 2022 25th Euromicro Conference on Digital System Design (DSD), 189–196, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD57027.2022.00034

Anantharajaiah, N.; Becker, J.

2023. 2022 25th Euromicro Conference on Digital System Design (DSD), 174–180, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD57027.2022.00032

Kempf, F.; Kühbacher, C.; Mellwig, C.; Altmeyer, S.; Ungerer, T.; Becker, J.

2023. 2022 25th Euromicro Conference on Digital System Design (DSD), 704–711, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD57027.2022.00099

Kreß, F.; Hoefer, J.; Hotfilter, T.; Walter, I.; El Annabi, E. M.; Harbaum, T.; Becker, J.

2023. Machine Learning and Principles and Practice of Knowledge Discovery in Databases. Hrsg.: I. Koprinska. Pt. 1, 557–568, Springer International Publishing. doi:10.1007/978-3-031-23618-1_37

Pazmino Betancourt, V. H.

2023. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000158306

Neubauer, K.

2023, January 19. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000154624

de Barros, J. B.; Anantharajaiah, N.; Ayala-Rincón, M.; Llanos, C. H.; Becker, J.

2022. Microprocessors and Microsystems, 94, Art.-Nr.: 104668. doi:10.1016/j.micpro.2022.104668

Sidorenko, V.; Fröhlich, I.; Müller, W. F. J.; Emschermann, D.; Bähr, S.; Sturm, C.; Becker, J.

2022. Journal of Instrumentation, 17, Art.-Nr.: C05008. doi:10.1088/1748-0221/17/05/C05008

Pfau, J.; Zaki, P. W.; Becker, J.

2022. Journal of Signal Processing Systems, 94, 865–882. doi:10.1007/s11265-022-01786-z

Guissouma, H.; Hohl, C. P.; Lesniak, F.; Schindewolf, M.; Becker, J.; Sax, E.

2022. IEEE Access, 10, 57696–57717. doi:10.1109/ACCESS.2022.3176879

Schade, F.; Karle, C.; Mühlbeier, E.; Gönnheimer, P.; Fleischer, J.; Becker, J.

2022. Procedia CIRP, 107, 1311–1316. doi:10.1016/j.procir.2022.05.150

Deiana, A. M.; Tran, N.; Agar, J.; Blott, M.; Di Guglielmo, G.; Duarte, J.; Harris, P.; Hauck, S.; Liu, M.; Neubauer, M. S.; Ngadiuba, J.; Ogrenci-Memik, S.; Pierini, M.; Aarrestad, T.; Bähr, S.; Becker, J.; Berthold, A.-S.; Bonventre, R. J.; Müller Bravo, T. E.; Diefenthaler, M.; et al.

2022. Frontiers in Big Data, 5, Art.Nr. 787421. doi:10.3389/fdata.2022.787421

Belle 2 Collaboration; Belle Collaboration; Abudinén, F.; Aggarwal, L.; Ahmed, H.; Aihara, H.; Akopov, N.; Al Said, S.; Aloisio, A.; Anh Ky, N.; Asner, D. M.; Atmacan, H.; Aushev, V.; Ayad, R.; Babu, V.; Bacher, S.; Baehr, S.; Bahinipati, S.; Bambade, P.; Becker, J.; et al.

2022. Journal of high energy physics, 2022 (2), Artikel-Nr.: 63. doi:10.1007/JHEP02(2022)063

Reuter, M.; Kramer, A.; Krauss, T.; Pfau, J.; Becker, J.; Hofmann, K.

2022. 2022 IEEE 40th Central America and Panama Convention (CONCAPAN), 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/CONCAPAN48024.2022.9997726

Dörr, T.; Schade, F.; Masing, L.; Becker, J.; Keramidas, G.; Antonopoulos, C. P.; Mavropoulos, M.; Kelefouras, V.; Voros, N.

2022. 2022 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Nicosia, Cyprus, 04-06 July 2022, 369–370, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI54635.2022.00081

Dörr, T.; Schade, F.; Ahlbrecht, A.; Zaeske, W.; Masing, L.; Durak, U.; Becker, J.

2022. 2022 IEEE/ACM 26th International Symposium on Distributed Simulation and Real Time Applications (DS-RT), 151–159, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DS-RT55542.2022.9932069

Schade, F.; Sandmann, T.; Becker, J.; Theiling, H.

2022. 2022 IEEE 28th International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA), Taipei, Taiwan, 23-25 August 2022, 228–234, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/RTCSA55878.2022.00031

Kempf, F.; Höfer, J.; Kreß, F.; Hotfilter, T.; Harbaum, T.; Becker, J.

2022. Conference Proceedings: 2022 IEEE 35th International System-on-Chip Conference (SOCC) Ed.: S. Sezer, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC56010.2022.9908110

Schade, F.; Dörr, T.; Becker, J.

2022. Conference Proceedings: 2022 IEEE 35th International System-on-Chip Conference (SOCC) Ed.: S. Sezer, 1–2, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC56010.2022.9908090

Nitzsche, S.; Pachideh, B.; Neher, M.; Kreutzer, M.; Link, N.; Theurer, L.; Becker, J.

2022. Conference Proceedings: 2022 Smart Systems Integration (SSI), 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SSI56489.2022.9901412

Hotfilter, T.; Kreß, F.; Kempf, F.; Becker, J.; Baili, I.

2022. 2022 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Nicosia, Cyprus, 04-06 July 2022, 371–372. doi:10.1109/ISVLSI54635.2022.00082

Siddiqui, F.; Khan, R.; Sezer, S.; McLaughlin, K.; Masing, L.; Dörr, T.; Schade, F.; Becker, J.; Ahlbrecht, A.; Zaeske, W.; Durak, U.; Adler, N.; Sailer, A.; Weber, R.; Wilhelm, T.; Nemeth, G.; Nemeth, G.; Morales, V.; Gomez, P.; Keramidas, G.; et al.

2022. 2022 IEEE 95th Vehicular Technology Conference: (VTC2022-Spring): Proceedings ; 19–22 June 2022, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/VTC2022-Spring54318.2022.9860859

Kreß, F.; Hoefer, J.; Hotfilter, T.; Walter, I.; Sidorenko, V.; Harbaum, T.; Becker, J.

2022. 18th International Conference on Distributed Computing in Sensor Systems (DCOSS), 133–140, IEEEXplore. doi:10.1109/DCOSS54816.2022.00034

Kreß, F.; Serdyuk, A.; Hotfilter, T.; Höfer, J.; Harbaum, T.; Becker, J.; Hamann, T.

2022. 2022 11th Mediterranean Conference on Embedded Computing (MECO). Ed.: IEEE, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MECO55406.2022.9797131

Karle, C. M.; Kreutzer, M.; Pfau, J.; Becker, J.

2022. HEART2022: International Symposium on Highly-Efficient Accelerators and Reconfigurable Technologies, Tsukuba Japan, June 9 - 10, 2022, 33–41, Association for Computing Machinery (ACM). doi:10.1145/3535044.3535049

Fasfous, N.; Vemparala, M. R.; Frickenstein, A.; Valpreda, E.; Salihu, D.; Höfer, J.; Singh, A.; Nagaraja, N.-S.; Voegel, H.-J.; Vu Doan, N. A.; Martina, M.; Becker, J.; Stechele, W.

2022. Proceedings of the 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE 2022). Ed.: C. Bolchini, 238–243, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE54114.2022.9774574

Masing, L.; Dörr, T.; Schade, F.; Becker, J.; Keramidas, G.; Antonopoulos, C. P.; Mavropoulos, M.; Tiganourias, E.; Kelefouras, V.; Antonopoulos, K.; Voros, N.; Durak, U.; Ahlbrecht, A.; Zaeske, W.; Panagiotou, C.; Karadimas, D.; Adler, N.; Sailer, A.; Weber, R.; Wilhelm, T.; et al.

2022. 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE), Antwerp, Belgium, 14-23 March 2022, 814–818, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE54114.2022.9774534

Hotfilter, T.; Kreß, F.; Kempf, F.; Becker, J.; Haro, J. M. De; Jiménez-González, D.; Moretó, M.; Álvarez, C.; Labarta, J.; Baili, I.

2022. 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE), Antwerp, Belgium, 14-23 March 2022, 628–631, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE54114.2022.9774716

Kiechle, V.; Börsig, M.; Nitzsche, S.; Baumgart, I.; Becker, J.

2022. Proceedings of the 8th International Conference on Information Systems Security and Privacy. Ed.: P. Mori. Vol. 1, 345–356, SciTePress. doi:10.5220/0010813500003120

Walter, I.; Ney, J.; Hotfilter, T.; Rybalkin, V.; Hoefer, J.; Wehn, N.; Becker, J.

2022. Machine Learning and Principles and Practice of Knowledge Discovery in Databases – International Workshops of ECML PKDD 2021, Virtual Event, September 13-17, 2021, Proceedings, Part I. Ed.: M. Kamp, 339–350, Springer International Publishing. doi:10.1007/978-3-030-93736-2_26

Albers, A.; Ovtcharova, J.; Becker, J.; Lanza, G.; Zhang, W.; Zhang, T.; Qiao, F.; Ma, Y.; Wang, J.; Wu, Z.; Ehrmann, C.; Gönnheimer, P.; Behrendt, M.; Mandel, C.; Stürmlinger, T.; Klippert, M.; Kimmig, A.; Schade, F.; Yang, S.; Heider, I.; et al.

2022. (J. Fleischer, Ed.), Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000143693

Wankler Hoppe, A.

2022, July 27. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000148789

Ardila Pérez, L. E.

2022, May 11. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000145595

Kimmig, A.; Schöck, M.; Mühlbeier, E.; Oexle, F.; Fleischer, J.; Bönsch, J.; Ovtcharova, J.; Hahn, J.; Grunwald, A.; Albers, A.; Rapp, S.; Hagenmeyer, V.; Scholz, S. G.; Schmidt, A.; Müller, T.; Becker, J.; Schade, F.; Beyerer, J.; Rehak, J.; Zwick, T.; et al.

2021. Zeitschrift für wirtschaftlichen Fabrikbetrieb, 116 (12), 935–939. doi:10.1515/zwf-2021-0207

Hoppe, A.; Kastensmidt, F. L.; Becker, J.

2021. Microelectronics Reliability, 126, Art.-Nr.: 114264. doi:10.1016/j.microrel.2021.114264

Dörr, T.; Sandmann, T.; Becker, J.

2021. Microprocessors and microsystems, 87, Article no: 104377. doi:10.1016/j.micpro.2021.104377

Dörr, T.; Sandmann, T.; Friederich, P.; Leitner, A.; Becker, J.

2021. Microprocessors and microsystems, 87, Aricle no: 104380. doi:10.1016/j.micpro.2021.104380

CBM Collaboration; Samanta, S.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; Caselle, M.; Sidorenko, V.; Trifonova, E.; Unger, K. L.; Weber, M.

2021. Nuclear physics <Amsterdam> / A, 1005, Art.-Nr.: 121896. doi:10.1016/j.nuclphysa.2020.121896

Bannwart Perina, A.; Silitonga, A.; Becker, J.; Bonato, V.

2021. IEEE transactions on computers, 70 (12), 2070–2082. doi:10.1109/TC.2021.3112260

Khan, N.; Nitzsche, S.; Lopez, A. G.; Becker, J.

2021. IEEE transactions on information forensics and security / Institute of Electrical and Electronics Engineers, 16, 2548–2563. doi:10.1109/TIFS.2021.3058777

CBM Collaboration; Ablyazimov, T.; Adak, R. P.; Adler, A.; Agarwal, A.; Agarwal, K.; Ahammed, Z.; Ahmad, A.; Ahmad, F.; Ahmad, N.; Akindinov, A.; Akishin, P.; Akishina, V.; Al-Turany, M.; Alekseev, I.; Alexandrov, E.; Alexandrov, I.; Becker, M.; Becker, K.-H.; Becker, J.; et al.

2021. Nuclear physics <Amsterdam> / A, 1005, Article no: 122089. doi:10.1016/S0375-9474(20)30414-0

Masing, L.; Lesniak, F.; Becker, J.

2021. IEEE embedded systems letters, 13 (1). doi:10.1109/LES.2020.2995084

Reuter, M.; Pfau, J.; Krauss, T. A.; Becker, J.; Hofmann, K.

2021. IEEE transactions on circuits and systems / 1, 68 (1), 114–125. doi:10.1109/TCSI.2020.3035889

Khan, N.; Castro-Godinez, J.; Xue, S.; Henkel, J.; Becker, J.

2021. IEEE transactions on very large scale integration (VLSI) systems, 29 (1), 38–50. doi:10.1109/TVLSI.2020.3023548

Neubauer, K.; Masing, L.; Mahl, M.; Becker, J.; Kramer, M.; Reichmann, C.

2021. Proceedings of the 2021 32nd International Workshop on Rapid System Prototyping: Shortening the Path from Specification to Prototype ; October 14, 2021, Virtual Conference, 29–35, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/RSP53691.2021.9806231

Pfau, J.; Reuter, M.; Hofmann, K.; Becker, J.

2021. 2020 International Conference on Field-Programmable Technology (ICFPT), Maui, HI, USA, 09-11 December 2020, 165–173, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ICFPT51103.2020.00031

Anantharajaiah, N.; Knopf, F.; Becker, J.

2021. Proceedings 34th IEEE International System-on-Chip Conference (SOCC): September 14–17, 2021, Virtual. Ed.: G. Qu, 248–253, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC52499.2021.9739596

Hotfilter, T.; Hoefer, J.; Kreß, F.; Kempf, F.; Becker, J.

2021. IEEE 34th International System-on-Chip Conference (SOCC), 14th-17th September 2021, Las Vegas, Nevada, USA, 83–88, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC52499.2021.9739212

Nitzsche, S.; Neher, M.; Dosky, S. von; Becker, J.

2021. Machine Learning and Principles and Practice of Knowledge Discovery in Databases: International Workshops of ECML PKDD 2021, Virtual Event, September 13-17, 2021, Proceedings, Part I. Ed.: M. Kamp, 390–396, Springer. doi:10.1007/978-3-030-93736-2_30

Becker, J.; Masing, L.; Dörr, T.; Schade, F.; Keramidas, G.; Antonopoulos, C. P.; Mavropoulos, M.; Tiganourias, E.; Kelefouras, V.; Antonopoulos, K.; Voros, N.; Durak, U.; Ahlbrecht, A.; Zaeske, W.; Panagiotou, C.; Karadimas, D.; Adler, N.; Sailer, A.; Weber, R.; Wilhelm, T.; et al.

2021. Proceedings 2021 31st International Conference on Field-Programmable Logic and Applications: FPL 2021 ; Dresden, Germany, 30 August – 3 September 2021, 382–383, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/FPL53798.2021.00075

Fasfous, N.; Vemparala, M.-R.; Frickenstein, A.; Badawy, M.; Hundhausen, F.; Höfer, J.; Nagaraja, N.-S.; Unger, C.; Vögel, H.-J.; Becker, J.; Asfour, T.; Stechele, W.

2021. 2021 IEEE International Conference on Robotics and Automation (ICRA): 30 May – 5 June 2021, Xi’an, China, 13430–13437, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ICRA48506.2021.9561045

Silitonga, A.; Kiyak, Y.; Becker, J.

2021. 2021 IEEE 15th International Conference on Anti-counterfeiting, Security, and Identification (ASID), 122–128, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ASID52932.2021.9651483

Neubauer, K.; Rumez, M.; Tremmel, H.; Hoppe, A.; Kriesten, R.; Nenninger, P.; Sax, E.; Becker, J.

2021. 2021 IEEE International Symposium on Systems Engineering (ISSE): 13 September - 13 October 2021, online, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISSE51541.2021.9582552

Schade, F.; Barton, D.; Fleischer, J.; Becker, J.

2021. 7th IEEE World Forum on Internet of Things (WF-IoT), 680–685, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/WF-IoT51360.2021.9595534

Dörr, T.; Sandmann, T.; Mohr, H.; Becker, J.

2021. 2021 24th Euromicro Conference on Digital System Design (DSD), 107–114, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD53832.2021.00026

Kempf, F.; Hartmann, T.; Bähr, S.; Becker, J.

2021. 2021 IEEE Computer Society Annual Symposium on VLSI (ISVLSI): 7-9 July 2021, Tampa, FL, USA, 7–12, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI51109.2021.00013

Hoppe, A.; Becker, J.; Kastensmidt, F. L.

2021. 2021 IEEE 12th Latin America Symposium on Circuits and System (LASCAS) : 12th IEEE Latin American Symposium on Circuits and Systems, LASCAS 2021, Arequipa, 22 February 2021 - 25 February 2021, Art.-Nr.: 9459137, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/LASCAS51355.2021.9459137

Pfau, J.; Zaki, P. W.; Becker, J.

2021. Applied Reconfigurable Computing. Architectures, Tools, and Applications: 17th International Symposium, ARC 2021, Virtual Event, June 29–30, 2021, Proceedings. Ed.: S. Derrien, 35–49, Springer-Verlag. doi:10.1007/978-3-030-79025-7_3

Anantharajaiah, N.; Zhang, Z.; Becker, J.

2021. Applied Reconfigurable Computing. Ed.: S. Derrien, 125–139, Springer Nature Switzerland. doi:10.1007/978-3-030-79025-7_9

Khan, N.; Hettwer, B.; Becker, J.

2021. Applied Reconfigurable Computing. Ed.: S. Derrien, 188–202, Springer Nature Switzerland. doi:10.1007/978-3-030-79025-7_13

Lesniak, F.; Kreß, F.; Becker, J.

2021. Applied Reconfigurable Computing. Ed.: S. Derrien, 221–231, Springer Nature Switzerland. doi:10.1007/978-3-030-79025-7_15

Silitonga, A.; Becker, J.

2021. The 14th IEEE International Systems Conference (SYSCON), Montreal, Canada (Virtual), 24-27 August, 2020, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SysCon47679.2020.9353653

Sidorenko, V.; Fröhlich, I.; Müller, W. F. J.; Emschermann, D.; Bähr, S.; Sturm, C.; Becker, J.

2021. doi:10.48550/arXiv.2110.12738

Becker, J.; Sax, E.; Stork, W.

2021

Khan, N. M.

2021, December 16. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000140875

Oszwald, F.

2021, October 12. KIT Scientific Publishing. doi:10.5445/KSP/1000132321

BM@N Collaboration; CBM Collaboration; NA61/SHINE Collaboration; Guber, F.; Finogeev, D.; Golubeva, M.; Ivashkin, A.; Izvestnyy, A.; Karpushkin, N.; Morozov, S.; Kugler, A.; Mikhaylov, V.; Senger, A.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; Caselle, M.; Sidorenko, V.; Trifonova, E.; et al.

2020. Nuclear instruments & methods in physics research / A, 958, Art.-Nr. 162728. doi:10.1016/j.nima.2019.162728

CBM Collaboration; Senger, P.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; Caselle, M.; Sidorenko, V.; Trifonova, E.; Unger, K. L.; Weber, M.

2020. International journal of modern physics / E, 29 (02), 2030001–1. doi:10.1142/S0218301320300015

CBM Collaboration; Senger, P.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; Caselle, M.; Sidorenko, V.; Trifonova, E.; Unger, K. L.; Weber, M.

2020. Physica scripta, 95 (7), Art.-Nr.: 074003. doi:10.1088/1402-4896/ab8c14

CBM Collaboration; Golosov, O.; Klochkov, V.; Kashirin, E.; Selyuzhenkov, I.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; Caselle, M.; Sidorenko, V.; Trifonova, E.; Unger, K. L.; Weber, M.

2020. Physics of particles and nuclei, 51 (3), 297–300. doi:10.1134/S1063779620030119

CBM Collaboration; Segal, I.; Lubynets, O.; Selyuzhenkov, I.; Klochkov, V.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; Caselle, M.; Sidorenko, V.; Trifonova, E.; Unger, K. L.; Weber, M.

2020. Journal of Physics: Conference Series, 1690, Art.-Nr.: 012107. doi:10.1088/1742-6596/1690/1/012107

CBM Collaboration; Golosov, O.; Klochkov, V.; Kashirin, E.; Selyuzhenkov, I.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; Caselle, M.; Sidorenko, V.; Trifonova, E.; Unger, K. L.; Weber, M.

2020. Journal of Physics: Conference Series, 1690, Art.-Nr. 012104. doi:10.1088/1742-6596/1690/1/012104

Belle 2 Collaboration; Abudinén, F.; Adachi, I.; Aihara, H.; Akopov, N.; Aloisio, A.; Ameli, F.; Anh Ky, N.; Asner, D. M.; Aushev, T.; Aushev, V.; Babu, V.; Baehr, S.; Bahinipati, S.; Bambade, P.; Banerjee, S.; Bansal, S.; Baudot, J.; Becker, J.; Behera, P. K.; et al.

2020. Physical review letters, 125 (16), Article: 161806. doi:10.1103/PhysRevLett.125.161806

Skambraks, S.; Bähr, S.; Becker, J.; Kiesling, C.; McCarney, S.; Meggendorfer, F.; Tonder, R. V.; Lukas Unger, K.

2020. Journal of physics / Conference series, 1525 (1), Art. Nr.: 012102. doi:10.1088/1742-6596/1525/1/012102

Belle 2 Collaboration; Adachi, I.; Ahlburg, P.; Aihara, H.; Akopov, N.; Aloisio, A.; Anh Ky, N.; Asner, D. M.; Atmacan, H.; Aushev, T.; Aushev, V.; Aziz, T.; Babu, V.; Baehr, S.; Bambade, P.; Banerjee, S.; Bansal, V.; Barrett, M.; Baudot, J.; Becker, J.; et al.

2020. Physical review letters, 124 (14), Article: 141801. doi:10.1103/PhysRevLett.124.141801

Belle 2 Collaboration; Abudinén, F.; Adachi, I.; Ahlburg, P.; Aihara, H.; Akopov, N.; Aloisio, A.; Ameli, F.; Andricek, L.; Anh Ky, N.; Asner, D. M.; Atmacan, H.; Aushev, T.; Aushev, V.; Aziz, T.; Azmi, K.; Babu, V.; Baehr, S.; Bahinipati, S.; Becker, J.; et al.

2020. Chinese physics / C, 44 (2), Article: 021001. doi:10.1088/1674-1137/44/2/021001

Hoppe, A.; Becker, J.; Kastensmidt, F. L.

2020. 2020 IEEE 33rd International System-on-Chip Conference (SOCC): 8-11 September 2020, Las Vegas, NV, USA (online), 219–224, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC49529.2020.9524751

Borsig, M.; Nitzsche, S.; Eisele, M.; Gröll, R.; Becker, J.; Baumgart, I.

2020. 2020 IEEE International Workshop on Information Forensics and Security (WIFS), 6-11 December 2020, online, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/WIFS49906.2020.9360889

Barros, J. B. de; Anantharajaiah, N.; Ayala-Rincon, M.; Llanos, C. H.; Becker, J.

2020. 2020 IEEE Nordic Circuits and Systems Conference (NorCAS), 1–7, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NorCAS51424.2020.9265134

Liu, B.; Betancourt, V. P.; Zhu, Y.; Becker, J.

2020. 2020 IEEE International Symposium on Systems Engineering (ISSE), Article no: 9272016, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISSE49799.2020.9272016

Kern, M.; Taspolatoglu, E.; Scheytt, F.; Glock, T.; Liu, B.; Betancourt, V. P.; Becker, J.; Sax, E.

2020. 6th IEEE International Symposium on Systems Engineering (ISSE 2020), Vienna, A, 12 October - 12 November 2020, Article no: 9272013, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISSE49799.2020.9272013

Betancourt, V. P.; Liu, B.; Becker, J.

2020. 2020 IEEE International Symposium on Systems Engineering (ISSE), 1–5, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISSE49799.2020.9272014

Betancourt, V. P.; Glock, T.; Kharitonov, A.; Kern, M.; Liu, B.; Sax, E.; Becker, J.

2020. 2020 IEEE International Systems Conference (SysCon), 1–7, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SysCon47679.2020.9275862

Stock, S. C.; Becker, J.; Grimm, D.; Hotfilter, T.; Molinar, G.; Stang, M.; Stork, W.

2020. Proceedings of Artificial Intelligence for Science, Industry and Society — PoS(AISIS2019), 026, Scuola Internazionale Superiore di Studi Avanzati (SISSA). doi:10.22323/1.372.0026

Baehr, S.; Unger, K. L.; Becker, J.; Meggendorfer, F.; Skambraks, S.; Kiesling, C.

2020. Proceedings of Artificial Intelligence for Science, Industry and Society — PoS(AISIS2019), 010, Scuola Internazionale Superiore di Studi Avanzati (SISSA). doi:10.22323/1.372.0010

Silitonga, A.; Gassoumi, H.; Becker, J.

2020. The 14th IEEE International Conference on Anti-counterfeiting, Security, and Identification (ASID), Xiamen, China (Virtual), Oct. 31-Nov. 1, 2020, 65–71, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ASID50160.2020.9271734

Dörr, T.; Sandmann, T.; Friederich, P.; Leitner, A.; Becker, J.

2020. 2020 23rd Euromicro Conference on Digital System Design (DSD), 630–637, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD51259.2020.00103

Dörr, T.; Sandmann, T.; Becker, J.

2020. 2020 23rd Euromicro Conference on Digital System Design (DSD), 596–603, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD51259.2020.00098

Pfau, J.; Reuter, M.; Harbaum, T.; Hofmann, K.; Becker, J.

2020. 2019 32nd IEEE International System-on-Chip Conference (SOCC), Singapore, 3-6 Sept. 2019, 294–299, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC46988.2019.1570548289

Ablikim, M.; Achasov, M. N.; Ai, X. C.; Albayrak, O.; Ambrose, D. J.; An, F. F.; An, Q.; Bai, J. Z.; Ferroli, R. B.; Ban, Y.; Becker, J.; Bennett, J. V.; Bertani, M.; Bian, J. M.; Boger, E.; Bondarenko, O.; Boyko, I.; Briere, R. A.; Bytev, V.; Cai, H.; et al.

2020. 30 Years of Bes Physics : Proceedings of the Symposium on 30 Years of Bes Physics. Ed.: editet M. Ye, 229–235, World Scientific Publishing. doi:10.1142/9789811217739_0033

Ablikim, M.; Achasov, M. N.; Albayrak, O.; Ambrose, D. J.; An, F. F.; An, Q.; Bai, J. Z.; Ferroli, R. B.; Ban, Y.; Becker, J.; Bennett, J. V.; Bertani, M.; Bian, J. M.; Boger, E.; Bondarenko, O.; Boyko, I.; Braun, S.; Briere, R. A.; Bytev, V.; Cai, H.; et al.

2020. 30 Years of Bes Physics : Proceedings of the Symposium on 30 Years of Bes Physics. Ed.: M. Ye, 236–242, World Scientific Publishing. doi:10.1142/9789811217739_0034

Liu, B.; Glock, T.; Betancourt, V. P.; Kern, M.; Sax, E.; Becker, J.

2020. 2020 9th International Conference on Industrial Technology and Management (ICITM), 78–83, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ICITM48982.2020.9080344

Neubauer, K.; Bucher, H.; Haas, B.; Becker, J.

2020. Proceedings of the 2020 Summer Simulation Conference, Society for Computer Simulation International, San Diego, CA, United States, Art.-Nr.: 31, Association for Computing Machinery (ACM)

Reuter, M.; Pfau, J.; Krauss, T. A.; Moradinasab, M.; Schwalke, U.; Becker, J.; Hofmann, K.

2020. Proceedings of the 11th IEEE Latin American Symposium on Circuits & Systems (LASCAS), San Jose, Costa Rica, February 15-28, 2020, Article No. 9069043, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/LASCAS45839.2020.9069043

Reder, S.; Becker, J.

2020. 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, France, 9-13 March 2020, 210–215, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE48585.2020.9116400

Hotfilter, T.; Kempf, F.; Becker, J.; Reinhardt, D.; Baili, I.

2020. 6th IEEE World Forum on Internet of Things, WF-IoT 2020, New Orleans, United States, 2 - 16 June 2020, Art.Nr. 9221396, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/WF-IoT48130.2020.9221396

Reder, S.; Becker, J.

2020. 26th IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS), 148–159, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/RTAS48715.2020.00-10

Unger, K. L.; Bähr, S.; Becker, J.; Iwasaki, Y.; Kim, K.; Lai, Y.-T.

2020. Proceedings of Topical Workshop on Electronics for Particle Physics, TWEPP 2019, Santiago de Compostela, Spain, 2 - 6 September 2019, Code 160323. doi:10.22323/1.370.0145

Oszwald, F.; Obergfell, P.; Liu, B. B.; Victor Pazmino; Becker, J.

2020. WCX 2020 SAE World Congress Experience, Detroit, MI, April 21-23, 2020. Proceedings. doi:10.4271/2020-01-1364

Oszwald, F.; Bertelo, R.; Gericota, M.; Becker, J.

2020. WCX SAE World Congress Experience, Detroit, MI, April 21-23, 2020. Proceedings. doi:10.4271/2020-01-1363

Bucher, H.

2020, December 1. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000126919

Masing, L. J.

2020, November 26. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000126812

Reder, S. T.

2020, October 7. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000124294

CBM Collaboration; Mikhaylov, V.; Kugler, A.; Kushpil, V.; Svoboda, O.; Tlustý, P.; Golubeva, M.; Guber, F.; Ivashkin, A.; Morozov, S.; Klochkov, V.; Selyuzhenkov, I.; Senger, A.; Bondarenko, S.; Burov, V.; Malakhov, A.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; et al.

2019. The European physical journal / Web of Conferences, 204, Art.-Nr.: 11004. doi:10.1051/epjconf/201920411004

CBM Collaboration; Karpushkin, N.; Finogeev, D.; Golubeva, M.; Guber, F.; Ivashkin, A.; Izvestnyy, A.; Ladygin, V.; Morozov, S.; Kugler, A.; Mikhaylov, V.; Senger, A.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; Caselle, M.; Sidorenko, V.; Trifonova, E.; Unger, K. L.; et al.

2019. Nuclear instruments & methods in physics research / A, 936, 156–157. doi:10.1016/j.nima.2018.10.054

CBM Collaboration; Senger, P.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; Caselle, M.; Sidorenko, V.; Trifonova, E.; Unger, K. L.; Weber, M.

2019. Particles, 2 (4), 499–510. doi:10.3390/particles2040031

Figuli, S. P. D.; Becker, J.

2019. Journal of circuits, systems, and computers, 28 (1), Art. Nr.: 1950015. doi:10.1142/S0218126619500154

Reder, S.; Kempf, F.; Bucher, H.; Becker, J.; Alefragis, P.; Voros, N.; Skalistis, S.; Derrien, S.; Puaut, I.; Oey, O.; Stripf, T.; Ferdinand, C.; David, C.; Ulbig, P.; Mueller, D.; Durak, U.

2019. Journal of aerospace information systems, 16 (11), 521–533. doi:10.2514/1.I010749

Gönnheimer, P.; Kimmig, A.; Mandel, C.; Stürmlinger, T.; Yang, S.; Schade, F.; Ehrmann, C.; Klee, B.; Behrendt, M.; Schlechtendahl, J.; Fischer, M.; Trautmann, K.; Fleischer, J.; Lanza, G.; Ovtcharova, J.; Becker, J.; Albers, A.

2019. Procedia CIRP, 84, 880–885. doi:10.1016/j.procir.2019.04.260

Yigui, L.; Youteng, S.; Schade, F.; Hotfilter, T.; Becker, J.; Yuan, Z.; Zizhou, O.; Weiming, L.

2019. Proceedings of the Institution of Mechanical Engineers / D, 233 (9), 2371–2378. doi:10.1177/0954407019851334

Bucher, H.; Kamm, S.; Becker, J.

2019. Simulation Notes Europe, 29 (2), 73–78. doi:10.11128/sne.29.tn.10472

Barton, D.; Gönnheimer, P.; Schade, F.; Ehrmann, C.; Becker, J.; Fleischer, J.

2019. Procedia CIRP, 81, 1331–1336. doi:10.1016/j.procir.2019.04.022

Oszwald, F.; Obergfell, P.; Meseth, M.; Chamas, M.; Traub, M.; Becker, J.; Sax, E.

2019. Proceedings of the 19th International Congress Electronics in Vehicles (ELIV), 16. - 17. Oktober 2019

Kempf, F.; Anantharajaiah, N.; Masing, L.; Becker, J.

2019. 32nd IEEE International System on Chip Conference, SOCC 2019; Singapore; Singapore; 3 September 2019 through 6 September 2019. Ed.: D. Zhao, 39–44, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC46988.2019.1570558594

Oszwald, F.; Obergfell, P.; Traub, M.; Becker, J.

2019. 32nd IEEE International System on Chip Conference, SOCC 2019; Singapore; Singapore; 3 September 2019 through 6 September 2019. Ed.: D. Zhao, 203–208, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC46988.2019.1570547977

Bannwart Perina, A.; Becker, J.; Bonato, V.

2019. 2019 International Conference on Field-Programmable Technology : ICFPT 2019 : Tianjin, China, 9-13 December 2019 : proceedings, 343–346, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ICFPT47387.2019.00063

Perina, A. B.; Becker, J.; Bonato, V.

2019. 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS 2019), 618–621, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ICECS46596.2019.8964669

Reuter, M.; Krauss, T. A.; Moradinasab, M.; Pfau, J.; Schwalke, U.; Becker, J.; Hofmann, K.

2019. Proceedings. 2019 IEEE Asia Pacific Conference on Circuits and Systems : Royal Orchind Sheraton Hotel and Towers Bangkok, Thailand, November 11-14, 2019, 113–116, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/APCCAS47518.2019.8953083

Anantharajaiah, N.; Kempf, F.; Masing, L.; Lesniak, F. M.; Becker, J.

2019. Proceedings of the 12th International Workshop on Network on Chip Architectures (NoCArc 2019), Columbus, OH, Ocober 12-13, 2019, 1–6, Association for Computing Machinery (ACM). doi:10.1145/3356045.3360718

Silitonga, A.; Jiang, Z.; Khan, N.; Becker, J.

2019. 2019 IEEE Nordic Circuits and Systems Conference (NorCAS), Helsinki, FIN, October 29-30, 2019, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NORCHIP.2019.8906923

Bucher, H.; Kamm, S.; Becker, J.

2019. Proceedings of the 51st Summer Computer Simulation Conference, SummerSim 2019, ACM, Art.-Nr. 18, Society for Computer Simulation International. doi:10.5555/3374138.3374156

Oszwald, F.; Obergfell, P.; Traub, M.; Becker, J.

2019. Proceedings of the 32nd IEEE International System-on-Chip Conference (SOCC), Singapur, 3 - 6 September 2019

Liu, B.; Glock, T.; Sax, E.; Pazmino Betancourt, V.; Kern, M.; Becker, J.

2019. Annual IEEE International Systems Conference, Orlando, USA, 8 - 11 April 2019

Baehr, S.; Poehler, J.; Unger, K.; Hochstuhl, A.; Becker, J.; Skambraks, S.; McCarney, S.; Meggendorfer, F.; Kiesling, C.

2019. Connecting the Dots and Workshop on Intelligent Trackers (CTD/WIT 2019), València, E, April 2-5, 2019

Khan, N.; Nitzsche, S.; Becker, J.

2019. 5th International Conference on Information Systems Security and Privacy, ICISSP 2019; Prague; Czech Republic; 23 February 2019 through 25 February 2019. Ed.: P. Mori, 564–571, SciTePress. doi:10.5220/0007576305640571

Masing, L.; Lesniak, F.; Becker, J.

2019. 15th International Symposium on Applied Reconfigurable Computing, ARC 2019; Darmstadt; Germany; 9 April 2019 through 11 April 2019, 319–333. doi:10.1007/978-3-030-17227-5_23

Khan, N.; Silitonga, A.; Pachideh, B.; Nitzsche, S.; Becker, J.

2019. Applied reconfigurable computing : 15th international symposium, ARC 2019, Darmstadt, Germany, April 9-11, 2019 : proceedings, 137–146, Springer. doi:10.1007/978-3-030-17227-5_11

Dörr, T.; Sandmann, T.; Schade, F.; Bapp, F. K.; Becker, J.

2019. Applied Reconfigurable Computing – 15th International Symposium, ARC 2019, Darmstadt, 9.-11. April 2019, 96–111, Springer. doi:10.1007/978-3-030-17227-5_8

Glock, T.; Betancourt, V. P.; Kern, M.; Liu, B.; Reiß, T.; Sax, E.; Becker, J.

2019. 8th International Conference on Industrial Technology and Management (ICITM 2019), Cambridge, UK, March 2-4, 2019

Bucher, H.; Neubauer, K.; Becker, J.

2019. WCX SAE World Congress Experience, Detroit, USA, April 9-11 2019, 14 S., SAE International. doi:10.4271/2019-01-0111

Bucher, H.; Kamm, S.; Becker, J.

2019. ASIM-Workshop Simulation Technischer Systeme / Grundlagen und Methoden in Modellbildung und Simulation, Braunschweig, Germany, 21. Februar 2019 - 22. Februar 2019. Ed.: U. Durak, 7–12, ARGESIM. doi:10.11128/arep.57

Belle 2 Collaboration; Bähr, S.; Becker, J.; Unger, K.

2019

Becker, J.; Grimm, D.; Hotfilter, T.; Meier, C.; Molinar, G.; Stang, M.; Stock, S.; Stork, W.

2019, October 22. Symposium Artificial Intelligence for Science, Industry and Society (AISIS 2019), Mexico City, Mexico, October 20–December 25, 2019

Harbaum, T.

2019. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000096122

Bapp, F.; Becker, J.

2018. Advances in Aeronautical Informatics : Technologies Towards Flight 4.0. Ed.: U. Durak, 17–27, Springer. doi:10.1007/978-3-319-75058-3_2

Durak, U. D.; Becker, J.; Hartmann, S.; Voros, N. S.

2018. Springer International Publishing. doi:10.1007/978-3-319-75058-3

CBM Collaboration; Kisel, I.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; Caselle, M.; Sidorenko, V.; Trifonova, E.; Unger, K. L.; Weber, M.

2018. Journal of Physics: Conference Series, 1070, 012015. doi:10.1088/1742-6596/1070/1/012015

Sotiriou-Xanthopoulos, E.; Masing, L.; Xydis, S.; Siozios, K.; Becker, J.; Soudris, D.

2018. ACM transactions on embedded computing systems, 17 (5), Article: 86. doi:10.1145/3242179

Oszwald, F.; Obergfell, P.; Traub, M.; Becker, J.

2018. 4th IEEE International Symposium on Systems Engineering, ISSE 2018; Rome Marriott Park HotelRoma; Italy; 1 October 2018 through 3 October 2018, Art. Nr.: 8544451, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SysEng.2018.8544451

Silitonga, A.; Schade, F.; Jiang, G.; Becker, J.

2018. Proceedings of the 16th IEEE International Symposium on Parallel and Distributed Processing with Applications (ISPA2018), Melbourne, Australia, 11th-13th December 2018, 1009–1016, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/BDCloud.2018.00147

Becker, J.; Prasanna, V. K.; Weimer, M.; Luk, W.; Aasaraai, K.; Chiou, D.

2018. 2018 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), Vancouver, CDN, May 21-25, 2018, 81–82, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/IPDPSW.2018.00021

Masing, L.; Srivatsa, A.; Kreß, F.; Anantharajaiah, N.; Herkersdorf, A.; Becker, J.

2018. IEEE 12th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), Hanoi, VN, September 12-14, 2018, 138–145, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC2018.2018.00033

Betancourt, V. P.; Glock, T.; Kern, M.; Sax, E.; Becker, J.

2018. VDI Automation 2018 - 19. Leitkongress der Mess- und Automatisierungstechnik Seamless Convergence of Automation & IT, Baden-Baden, 03.-04. Juli 2018, embeX GmbH

Oszwald, F.; Becker, J.; Obergfell, P.; Traub, M.

2018. 32nd IEEE International Parallel and Distributed Processing Symposium Workshops, IPDPSW 2018; Vancouver; Canada; 21 May 2018 through 25 May 2018, 206–209, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/IPDPSW.2018.00039

Baehr, S.; Kempf, F.; Becker, J.

2018. Proceedings of the 18th International Conference on Nanotechnology (IEEE-NANO 2018), Cork, IRL, July 23-26, 2018, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NANO.2018.8626239

Baehr, S.; Kempf, F.; Becker, J.

2018. Proceedings of the 31th IEEE International System-on-Chip Conference (SOCC), Arlington, VA, September 4-7, 2018, 174–179, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC.2018.8618563

Harbaum, T.; Balzer, M.; Becker, J.; Weber, M.

2018. Proceedings of the 31th IEEE International System-on-Chip Conference (SOCC), 118–123, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC.2018.8618493

Bucher, H.; Becker, J.

2018. IEEE International Systems Engineering Symposium (ISSE), Rome, I, October 1-3, 2018, 1–8, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SysEng.2018.8544434

Alefragis, P.; Theodoridis, G.; Katsimpris, M.; Valouxis, C.; Gogos, C.; Goulas, G.; Voros, N.; Reder, S.; Kasnakli, K.; Bednara, M.; Müller, D.; Durak, U.; Becker, J.

2018. Applied Reconfigurable Computing - Architectures, Tools, and Applications, Proceedings of the 14th International Symposium, ARC 2018, Santorini, Greece, 2nd - 4th May 2018. Ed.: C. Antonopoulos, 700–711, Springer. doi:10.1007/978-3-319-78890-6_56

Becker, J.; Bapp, F. K.

2018. Applied Reconfigurable Computing - Architectures, Tools, and Applications, Proceedings of the 14th International Symposium, ARC 2018, Santorini, Greece, 2nd - 4th May 2018. Ed.: G. Keramidas, 685–699, Springer. doi:10.1007/978-3-319-78890-6_55

Glock, T.; Groß, T.; Kern, M.; Betancourt, V. P.; Sax, E.; Becker, J.

2018. 7th International Conference on Industrial Technology and Management (ICITM), Oxford, UK, March 7-9, 2018, 71–77, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ICITM.2018.8333922

Oey Oliver; Rückauer, M.; Stripf, T.; Becker, J.; David, C.; Debray, Y.; Müller, D.; Durak, U.; Kasnakli, E. K.; Bednara, M.; Schöberl, M.

2018. 9th European Congress - Embedded Real Time Software and Systems - ERTS² 2018, Toulouse, F, January 31- February 2, 2018

Pfau, J.; Figuli, S. P. D.; Bähr, S.; Becker, J.

2018. Applied Reconfigurable Computing - Architectures, Tools, and Applications, Proceedings of the 14th International Symposium, ARC 2018, Santorini, Greece, 2nd - 4th May 2018. Ed.: Nikolaos Voros, 615–626, Springer. doi:10.1007/978-3-319-78890-6_49

Reder, S.; Masing, L.; Bucher, H.; Braak, T. ter; Stripf, T.; Becker, J.

2018. Proceedings of the 2018 Design, Automation & Test in Europe (DATE) : 19-23 March 2018, Dresden, Germany. Ed. J. Madsen, 943–948, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE.2018.8342145

Hoppe, A. W.; Kastensmidt, F. L.; Becker, J.

2018. Proceedings of the 13th International Symposium on Applied Reconfigurable Computing, ARC 2018, Santorini, Greece, 2nd - 4th May 2018

Becker, J.; Bapp, F.

2018. Proceedings of the 14th International Symposium on Applied Reconfigurable Computing, ARC 2018, Santorini, Greece, 2nd - 4th May 2018

Bapp, F. K.; Dörr, T.; Sandmann, T.; Schade, F.; Becker, J.

2018. SAE International. doi:10.4271/2018-01-1072

Masing, L.; Srivatsa, A.; Kreß, F.; Anantharajaiah, N.; Herkersdorf, A.; Becker, J.

2018. 12th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC 2018), Hanoi, Vietnam, September 12–14, 2018

Figuli, R. P.

2018. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000080734

Bapp, F. K.

2018. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000079234

CBM Collaboration; Malygina, H.; Friese, V.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; Caselle, M.; Sidorenko, V.; Trifonova, E.; Unger, K. L.; Weber, M.

2017. Journal of Physics: Conference Series, 898, Art.-Nr.: 042022. doi:10.1088/1742-6596/898/4/042022

CBM Collaboration; Friese, V.; Bähr, S.; Balzer, M.; Becker, J.; Blank, T.; Caselle, M.; Sidorenko, V.; Trifonova, E.; Unger, K. L.; Weber, M.

2017. Journal of Physics: Conference Series, 898, Art.-Nr. 112003. doi:10.1088/1742-6596/898/11/112003

Figuli, S.; Figuli, P.; Sonnino, A.; Becker, J.

2017. International Journal of Advances in Telecommunications, Electrotechnics, Signals and Systems, 6 (2), 80–88

Derrien, S.; Atasu, K.; Cardoso, J. M. P.; Becker, J.

2017. Journal of signal processing systems, 88 (2), 103–105. doi:10.1007/s11265-017-1237-7

Meder, L. D.; Emschermann, D.; Frühauf, J.; Müller, W. F. J.; Becker, J.

2017. IEEE transactions on nuclear science, 64 (7), 1975–1982. doi:10.1109/TNS.2017.2713524

Bähr, S.; Skambraks, S.; Neuhaus, S.; Kiesling, C.; Becker, J.

2017. Journal of Instrumentation, 12, Art. Nr.: C03065. doi:10.1088/1748-0221/12/03/C03065

Meder, L.; Lebedev, J.; Becker, J.

2017. Journal of Instrumentation, 12 (3), Art. Nr.: C03074. doi:10.1088/1748-0221/12/03/C03074

Ablyazimov, T.; Abuhoza, A.; Adak, R. P.; Adamczyk, M.; Agarwal, K.; Aggarwal, M. M.; Ahammed, Z.; Ahmad, F.; Ahmad, N.; Ahmad, S.; Akindinov, A.; Akishin, P.; Akishina, E.; Akishina, T.; Akishina, V.; Akram, A.; Al-Turany, M.; Alekseev, I.; Becker, K.-H.; Becker, J.; et al.

2017. The European physical journal / A, 53 (3), 60. doi:10.1140/epja/i2017-12248-y

Sander, O.; Bapp, F.; Dieudonne, L.; Sandmann, T.; Becker, J.

2017. CEAS Aeronautical Journal, 8 (1), 143–155. doi:10.1007/s13272-016-0228-x

Harbaum, T.; Schade, C.; Damschen, M.; Tradowsky, C.; Bauer, L.; Henkel, J.; Becker, J.

2017. 2017 30th IEEE International System-on-Chip Conference (SOCC), Munich, 5–8 September 2017, 153–158, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC.2017.8226027

Becker, J.

2017. 2017 30th IEEE International System-on-Chip Conference (SOCC), Munich, Germany, 5–8 September 2017, 1 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC.2017.8225988

Bapp, F.; Becker, J.; Beyerer, J.; Doll, J.; Filsinger, M.; Frese, C.; Hubschneider, C.; Lauber, A.; Müller-Quade, J.; Pauli, M.; Roschani, M.; Salscheider, O.; Rosenhahn, B.; Ruf, M.; Stiller, C.; Willersinn, D.; Ziehn, J. R.

2017. TÜV-Tagung Fahrerassistenz, 2017, München, 8 S

Figuli, S. P. D.; Figuli, P.; Becker, J.

2017. Proceedings of the 40th International Conference on Telecommunications and Signal Processing, TSP 2017, Barcelona, Spain, 5th - 7th July 2017, 532–537, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/TSP.2017.8076044

Oey, O.; Rueckauer, M.; Stripf, T.; Becker, J.

2017. Embedded World Conference 2017, 14. bis 16. März 2017, Nürnberg

Derrien, S.; Puaut, I.; Alefragis, P.; Bednara, M.; Bucher, H.; David, C.; Debray, Y.; Durak, U.; Fassi, I.; Ferdinand, C.; Hardy, D.; Kritikakou, A.; Rauwerda, G.; Reder, S.; Sicks, M.; Stripf, T.; Sunesen, K.; Ter Braak, T.; Voros, N.; Becker, J.

2017. Proceedings of the 20th Design, Automation and Test in Europe, Lausanne, Switzerland, 27-31 March 2017, 286–289, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE.2017.7927000

Bucher, H.; Reichmann, C.; Becker, J.

2017. SAE World Congress Experience, WCX 2017, Detroit, United States, 4th - 6th April 2017, 14 S., SAE International. doi:10.4271/2017-01-0006

Figuli, P.; Ding, W.; Figuli, S.; Siozios, K.; Soudris, D.; Becker, J.

2017. 13th International Symposium on Applied Reconfigurable Computing, ARC 2017; Delft; Netherlands; 3 April 2017 through 7 April 2017. Ed. : S. Wong, 141–153, Springer International Publishing. doi:10.1007/978-3-319-56258-2_13

Weller, D.; Oboril, F.; Lukarski, D.; Becker, J.; Tahoori, M.

2017. FPGA ’17 Proceedings of the 2017 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, Monterey, CA, February 22 - 24, 2017, 247–256, Association for Computing Machinery (ACM). doi:10.1145/3020078.3021730

Friederich, S.

2017. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000078077

Bruckschlögl, T.

2017. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000073629

Meder, L. D.

2017. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000071051

Lari, V.; Weichslgartner, A.; Tanase, A.; Witterauf, M.; Khosravi, F.; Teich, J.; Heißwolf, J.; Friederich, S.; Becker, J.

2016. Information technology, 58 (6), 309–328. doi:10.1515/itit-2016-0022

Meder, L.; Dreschmann, M.; Sander, O.; Becker, J.

2016. Journal of Instrumentation, 11 (2), Art. Nr.: C02001. doi:10.1088/1748-0221/11/02/C02001

Bucher, H.; Buciuman, M.-F.; Klimm, A.; Sander, O.; Becker, J.

2016. EAI Endorsed Transactions on Security and Safety, 16 (8), Art.Nr. e1. doi:10.4108/eai.24-8-2015.2261038

Zaib, A.; Wild, T.; Herkersdorf, A.; Heisswolf, J.; Becker, J.; Weichslgartner, A.; Teich, J.

2016. Journal of systems architecture, 77, 72–82. doi:10.1016/j.sysarc.2017.03.004

Baehr, S.; Sander, O.; Heck, M.; Feindt, M.; Becker, J.

2016. Journal of Instrumentation, 11 (1), Art. Nr.: C01058. doi:10.1088/1748-0221/11/01/C01058

Birk, M.; Kretzek, E.; Figuli, P.; Weber, M.; Becker, J.; Ruiter, N. V.

2016. IEEE transactions on parallel and distributed systems, 27 (2), 455–467. doi:10.1109/TPDS.2015.2405508

Nürnberg, T.; Beuth, T.; Becker, J.; Puente León, F.

2016. International journal of electrical engineering education, 53 (2), 99–113. doi:10.1177/0020720915611439

Werner, S.; Lauber, A.; Koedam, M.; Becker, J.; Sax, E.; Goossens, K.

2016. International journal of online engineering, 12 (9), 52–60. doi:10.3991/ijoe.v12i09.6142

Pistorius, F.; Lauber, A.; Pfau, J.; Klimm, A.; Becker, J.

2016. SAE technical papers, 2016-April, 1–11. doi:10.4271/2016-01-0150

Becker, J.

2016. 2016 29th IEEE International System-on-Chip Conference (SOCC), Seattle, WA, USA, 6–9 September 2016, 1 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC.2016.7905493

Becker, J.

2016. 2016 29th IEEE International System-on-Chip Conference (SOCC), Seattle, WA, USA, 6–9 September 2016, 1 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC.2016.7905438

Pande, P.; Becker, J.

2016. 2016 29th IEEE International System-on-Chip Conference (SOCC), Seattle, WA, USA, 6–9 September 2016, 1–2, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC.2016.7905411

Chrzanowska-Jeske, M.; Becker, J.